U8110 Schematics

254 5 627KB

English Pages 13

Recommend Papers

- Similar Topics

- Chemistry

File loading please wait...

Citation preview

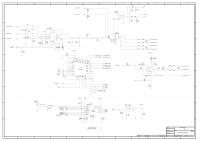

9. CIRCUIT DIAGRAM

1

2

3

5

4

6

7

9

8

10

12

11

A

A

G4 G3

TX

RX G2 G1

WCDMA_TX

ANT

C1012 22p

WCDMA_RX

N1002 DFYK61G95LBNCB

B

B C1013

RF

22p

DCS_TX WCDMA

ANT

VC2 VC1

VDD

2

5

R1001

R1006

NA

0 R1005

ANTSW2

0 R1004

ANTSW1

i b 0

R1003

ANTSW0

0

D

C1007 0.01u

C1001 10p

C1009 10p

C1002 0.01u

C1008 10p

o M

E VDD_A VDD_B

C1003 0.01u

C1000 6.8p ANTPAD

ANT

L1001 12nH

L1002 5.6nH

C DCS_RX

GSM_RX

D

C1005 10p

E

R1810

VCCA

0 R1811

VCCB

0 C1811 4.7u

C1802 10u 2012

N1800 LP2985AIBP-2.8 5

ON_OFF

GND

NA

BYPASS

R1800

4

VIN

VOUT

NA

VBATI

C1004 0.01u

C1810 10u 2012

R1804

EXTLDO F

11

G2 G1

h lc

51

ANTSW3

9 10

1

C1011 22p

R1007 1

GSM900_TX

16 4 2

N1000 LMSP54MA-213

8

6

VCG

GND4 GND3

R1002 NA

C1010 1000p

14 GSM900_RX GSM1800_1900_TX

3

GND1 GND5

4

V1001 RN47A4

VCCB

GND2

GSM1900_RX

15 13 5 7 3

GSM1800_RX

12

C

W1001 KMS-507

s ip

GSM_TX

1 2

F R1801

3

NA

NA

C1800 0.1u

C1801 1000p

R1825

0

R1850

2

0

3 C1850 0.1u

C1852 10u 2012

VOUT

LP3981ILD-2.8 6 VEN

VIN

BYPASS

VOUT_SE

7 GND2

N1850 1

G

V_wivi_A

0

R1851

R1826

V_wivi_B

0

5

G

4 GND1 C1851 0.033u

H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP 1

Drawn by: SG Kang

R&D CHK:

1

2

3

4

5

6

7

- 235 -

Schematics & manuals on www.mobilchips.com ___Mobilchips__

8

9

Time Changed:

Tuesday, September 04, 2003

10

QA CHK:

A2

ANT SW to ANT

DOC CTRL CHK:

Date Changed:

Size:

TITLE:

12 1 8 A

U8100 PT V1.3 Staggered AMD

MFG ENGR CHK: Changed by: SG Kang

H

LG ELECTRONICS INC.

SG Kang

REV:

Drawing Number:

Page: 1

5:01:55 pm

11

12

9. CIRCUIT DIAGRAM

1

2

3

4

5

6

7

8

9

12

11

10

A

A

Z1420 TMX-M453 6

IN-

5 4

C1441 2200p

IN+

SHIELD

GND

OUT+

OUT-

C1443 1.2p

1 2 3

C1442 2200p

L1441 100nH

B

B

1608

s ip

C1453

VCCB

C1454

0.01u

0.01u C1422 27p

C1423 27p

C1451 C1452

0.01u

0.01u R1410 0

R1401 0

L1760 1uH

L1422 68nH

C

h lc

C1448 C1447 0.01u 0.01u R1411 3.3K

L1421 68nH C1425 2200p

10

C1431 22p

i b

22p

L1401 2.2nH

L1411 6.8nH

C1402 1000p

o M 5 4 G3

O1

O2

1 2 3

IN

LK20A

G1

Z1400

E

C1413 1.2p

G2

6

C1412 1.2p

C1407 22p

L1402 NA

TP1401 TP1402 TP1403

WDAT F WCLK WSTR

N1400 LZT-108-5323

VCCREF XOIA XOIB VCCBUS IFLOA IFLOB GNDRFLO RFLOOA XOOA XOOB GNDREF GNDBUS REFON GNDVCO

INDBYP RFOUT VCCPLL VCCPHD PHDOUT VTUNE VCCVCO VCCRFLO RFLOOB XOOON RXON GNDPLL GNDPHD GNDTUNE

C1401

IFOUTB VCCMIX MIXINA MIXINB GNDBIAS GNDEME RFIN GNDBYP VCCRF GNDIF DATA CLK STROBE GLNA

C1776 4.7p

B10 C10 D10 E10 F10 G10 H10 J10 C8 D8 E8 F8 G8 H8

C

330p

47p

C1773 4.7p

B1770 TSX-8A

VCCB

R1770

10K

V1770

VCXOCONT

1K C1770 0.01u

BBY58-02W 4

3 HOT2

GND2

2 GND1

HOT1 1

13MHz

R1771

C1778

D 56p R1772 10K

IFLO IFLOBAR RFLO RFLOBAR XOOA XOOB E

R1740 C1740 0.01u

C1741 22p

C1730 0.01u

C1731 22p

VCCB

10

R1730

0 C1721 390p

C1772

C1751 22p

R1721 R1720 5.6K

C1777

C1750 22p

R1505 NA

K2 K3 K4 K5 K6 K7 K8 K9 K10 H3 H4 H5 H6 H7

B1 C1 D1 E1 F1 G1 H1 J1 K1 C3 D3 E3 F3 G3

D

C1400 NA

IFOUT GNDMIX VCCIF IFINA IFINB VCCLF QRA QRB IRA IRB CDQ CDI GNDLF MCLK

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C4 C5 C6 C7

C1444 22p

WCDMA_RX

MCLK

C1761 82p

R1430

1608

C1424 22p

RXIB

C1760 0.01u

1608

C1404 C1414 0.01u 22p

RXIA

0

0 NA

C1403 22p

RXQB

R1760

C1421

R1440

RXQA

10

C1722 NA

R1723

F

WRFLOOP

0 C1720 5600p

R1431

GPRFCTRL

0 R2108

CLKREQ

100 FROM MARITA SIDE FOR POWER SAVING

G

G

H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP 1

Drawn by: SG Kang

R&D CHK:

1

2

3

4

5

6

7

- 236 -

8

9

Time Changed:

Tuesday, September 04, 2003

12 1 8 A

U8100 PT V1.3 Staggered AMD REV:

QA CHK:

A2

UMTS RX (WOPY)

DOC CTRL CHK:

Date Changed:

Size:

TITLE:

MFG ENGR CHK: Changed by: SG Kang

Drawing Number:

Page:

12:50:11 pm

10

H

LG ELECTRONICS INC.

SG Kang

2

11

12

9. CIRCUIT DIAGRAM

1

2

3

5

4

6

7

10

9

8

11

12

A

A

WCDMA_TX

OUT

GND4 GND3

GND1

IN

GND2

N1650 CE0401G95DCB000-TT1

R1633 NA

VBATI

B

B R1630

VCCWPA

s ip

R1629

0 N1630

14

9

10

11

RFOUT

GND4 13

R1623

N1620 MAX1820ZEBC

0

A1

0

GND3

RF9266

12

0

R1621

WDCDCREF

A2

R1997

GND5

VDETECT

GND6

VCC_DET

GND7

GND2

8

A3

0

VBATI 7

C1636 NA

6

17 18

VCC22

VCC_BIAS1 GND1

GND8 VCC11

VCTRL2

VCC12

VCTRL1 RFIN

GND9

22 GND10 23 GND11

20

21

19 C1631 10p

4

h lc

3 2 1

R1617

0

WPAREF

0 C1635 NA

RFLO

RFLOBAR

i b

V_wivi_A

L1507 75

D

C1514 0.01u

B1501

V_wivi_A

4

E

5

V+

VO

3

RTEMP

o M Z1500 SX-S205B

GND1 2 GND2 NC 1

1 2 3

R1605 0

LM20BIM7X

R1606 NA

L1506 NA

R1604 NA

G1

S_OUT

G2

B_IN2 G3

B_IN1

6

5 4

C1513 0.01u

BLM15BB750SN1J

C1511 10p

R1503 0

0

GND

PGND

C1501 47p

C1512 10p

L1503 5.6nH

C1510 0.01u

C4

C1623 10u

C1715 100p

VCCWPA 3838 L1621

R1627

4.7uH C1627 4.7u

2.2p

L1505 10nH

C1507 4p

C1505 22p

R1502 680 L1501

J2 J3 J4 J5 J6 J7 J8 J9 J10 H3 H4 H5 H6 H7

15nH

R1628 100K

L1602

C1628 1000p

L1603

C

L1604 NA L1605 NA

IFLOBAR IFLO

C1714 100p

NA

C1716 4.7p

D

R1701

V_wivi_B

10 C1702 22p

C1701 0.01u

C1602 22p

C1601 0.01u

C1509 10p

R1603

OUT OUTBAR GNDRF MIXOUT MIXOUTBAR VCCIF IFBP IFBPBAR VTUNERF GNDRFLO2 GNDRF1 GNDRF2 GNDRF3 GNDIF

V_wivi_A

0

C1504 10p

C1508

WPOWERSENSE

39K L1601

C1624 4.7u

L1720

L1504 8.2nH

TP1701 TP1702

XOOA XOOB TP1504 TP1503 TP1502 TP1501

N1700 LZT-108-5322

E

QINBAR QIN INBAR IN VCCBB VCCIFPHD PHDIFOUT VCCIFPLL GNDIFVCO1 VCCIFVCO CLK GNDIFPHD GNDIFPLL WON

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C4 C5 C6 C7

TXQB TXQA TXIB TXIA C1503 22p R1702 10

C1704 22p

V_wivi_B WDAT

C1703 0.01u

WCLK WSTR

H8 G8 F8 E8 D8 C8 I10 H10 G10 F10 E10 D10 C10 B10

C1502 4p

F

L1502 15nH R1710

R1711

R1504 680

0 C1712 NA

R1703

V_wivi_B

C1

C3

R1510 0

R1501

V_wivi_A F

LX

C1626 330p

0

R1632

REF

B1

C2

G3 F3 E3 D3 C3 J1 I1 H1 G1 F1 E1 D1 C1 B1

16

5

BATT

GNDRFLO1 GNDIFLO DATA GNDBUS GNDBB VCCRF RFLOBAR RFLO VCCIFLO IFLOBAR IFLO VCCBUS XOOC XOOB

C1632 0.01u

VCC_BIAS2

_SHDN

OUT

GNDRFVCO2 STROBE GNDRFPLL TXON GNDRFPHD GNDRFVCO1 GNDTUNERF VCCRFVCO VCCRFPLL PHDRFOUT VCCRFPHD GNDIFVCO2 GNDTUIF VTUNEIF

C

VCC21

B4

SYNC

COMP

C1622 22p

R1631 15

A4

R1626 33K

_SKIP

4.7K C1710 150p

C1711 3300p

0

G

G

H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP 1

Drawn by: SG Kang

R&D CHK: DOC CTRL CHK:

1

2

3

4

5

6

7

- 237 -

8

9

Date Changed:

Time Changed:

Tuesday, September 04, 2003

10

Size:

TITLE:

MFG ENGR CHK: Changed by: SG Kang

H

LG ELECTRONICS INC.

SG Kang

UMTS TX (WIVI) to ISOLATOR

12 1 8 A

U8100 PT V1.3 Staggered AMD REV:

QA CHK:

A2

Drawing Number:

Page:

5:04:02 pm

3

11

12

9. CIRCUIT DIAGRAM

1

2

4

3

6

5

9

8

7

10

11

12

A

A

VBATI

BLM31PG601SN1

B

B

L1300

C1315 C1311 10u 10u 2012 2012

R1301 0

C1312 0.01u

C1313 22p

s ip

VDDBUF R1327

PASENSE+

0 C1326 NA

R1326

VDIG

0.05

R1325

PASENSE-

R1151

0

PAREG R1329 1K

C1322

IOUT

0

NA

R1321 1K

C1323 1200p

R1323 NA

0

C1325 100p

V1330 2SD2216J NA R1324 NA

C1320 470p

VDDPA R1338

B2

1

6

BGND0

GND7

GND1 BGND1

22p

22p

22p

C1336 NA

4

N1331 LDB211G8020C

NC

GND1 UB GND1

R1340 560

B1

3

L1331 15nH

C1333 10p

RXON BSEL0

L1230

R1334 R1213 R1212 R1211

MODC R1210

MODD

100

100

100

K2 K3 K4 K5 K6 K7 K8 K9 K10 H3 H4 H5 H6 H7

L1200 100

VCCA C1205 22p

C1201 0.01u C1271

XOOB R1272 NA

F

1000p L1201 5.6nH 1608 C1270

XOOA

4 6

10p

L1100 3.9nH

E3 R1140 100K

C1100

IN

2

O2

DCS_RX

10p

G1 G2 G3

L1101 3.3nH

C1115 NA

C1101 10p

A1 B1 C4 E8 F4 F7 G3 G4 H8

C3 B3 A3

C

VDIG R1150 0

VDIG_HERTA C1150 0.01u

C1151 NA

C1153 NA

C1155 NA

C2 C1 D4

D

E2 H2 H3 B2 E1

REXT VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9

QDATA IDATA DCLK

H4 AUXO2 G5 BEARP H5 BEARN G7 PCMUL E6 GPDAT E5 GPCLK

AUXI1 CCO MICIP DAC01 MICIN DAC02 GPA0 GPA1 DAC03 GPA2 N1101 GPA3 LZT-108-5321 DACCLK GPA4 DACDAT GPA5 DACSTR GPA6 GPA7 DEC1 H7 PCMDL DEC2 F6 PCMCLK DEC3 G6 PCMSYN DEC4 E7 DEC5 ADSTR

VCCA

C1114 7p

Z1100

O1

A2 VDD1 B5 VDD2 B7 VDD3 F5 VDD4 F8 VDD5 H6 VDD6

C1140 C1143 0.068u 0.068u

C1144 C1142 0.068u C1141 0.068u 0.068u

VDIG_HERTA

G2 NC1 H1 NC2

C1112 33p L1110 18nH

E Z1110 B7705

3 2 O1 G1 IN

C1110 1

O2 G2

C1111

4

GSM_RX

33p

5

L1111 10nH

1000p

NC5 MODA MODB MODC MODD VCCPLL XOOB XOOC NC6 GNDBUF NC3 PS GNDPLL XOOLA

33p

R1121 NA

N1100 LZT-108-5325

RFHD RFHC GNDRF RFLB RFLA VCCRF QRB QRA IRB IRA REON CLK DATA STROBE

L1120

VCCA

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C4 C5 C6 C7

C1104 0.01u

C1103 22p

R1103

R1250

R1104

0

0

R1105 0

F

R1106 0

R1240

H8 G8 F8 E8 D8 C8 J10 H10 G10 F10 E10 D10 C10 B10

R1273 NA

C1231 NA

B7714

C1102

D5 QDAT A4 IDAT C5 DCLK

G3 F3 E3 D3 C3 K1 J1 H1 G1 F1 E1 D1 C1 B1

MODB

C1230 NA

PCTL BSEL RXON TXON GNDPLANE TXOHA TXOHB VCCBUF TXOLA TXOLB GNDRF2 RFHB RFHA GNDRF1

0

MODA

PULSESKIP

C1330 22p

o M

C1331 22p

E PCTL

B2

1

C1327 33p

GND2

BLM15BB750SN1J

10

R1113

E4 F2 F3 G1 B8 B6 C6 C7 C8 D6 D8 D7

0

18

NC4 GNDVAR GNDVCO5 GNDVCO4 GNDVCO3 GNDVCO2 PHDOUT VTUNE VCCVCO GNDVCO6 GNDSILENT NC2 NC1 GNDVCO1

0

6

1

R1342 560

R1333

TXON

5

R1335

R1341

C1334

2

4 3 2

L1332 75

75 C1113

i b

5

L1333

C1335

L1330 33nH

R1332 0

19

2

BGND5

3

1 3 5

7

8

VCC2

VCC1

GND2

DCS_PCS_IN

14

22

EGSM_IN

N1300 CX77304-16

DCS_PCS_OUT

17

13

C1350 NA

C1351 NA

GND6

BGND2 GND3

EGSM_OUT

16

11 12

L1350 2.2nH

10p

BGND4 GND5

9 10

GND4

21

R1337 NA C1332

B1

33p

BS

C1340 NA

1.8nH

GND8

C1342 NA L1340

33p C1352

DCS_TX

APC

GSM_TX

15

C1343 NA C1341

D

BGND3

20

R1339 NA

4

UB

0

C1324 100p

TP1143

TP1142

AVDD

A8 IRA A7 IRB A6 QRA A5 QRB B4 RXSTR

RXON

N1330 LDB21897M15C

C1300 0.068u

NC

VSSPA

GND2

0

TP1141 F1

D3 I2CDAT D1 I2CCLK G8 MCLK D2 RESETB

TP1151 TP1152

h lc

C1321 470p

R1302

C1156 0.01u

I2CDAT I2CCLK SYSCLK2 RESOUT3n

R1328 NA

150p

FF_IN EXPOUT

5

VDIG

R1322

6

C

R1320

GPRFCTRL 0 C1240 NA

0 C1250 NA

RADCLK

TP1201 L1220

G

VLOOP

R1220

0

560 C1221 0.01u

C1225

C1220 NA

G RADSTR

TP1203 R1222

1800p

RADDAT

TP1202

2012

100uH

R1224

120 C1224 1200p

L1202

R1223 390 C1222 560p

VCCA C1203 22p

C1223 330p

C1202 0.01u

H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP 1

Drawn by: JS Joo

R&D CHK:

1

2

3

4

5

6

7

- 238 -

8

9

Time Changed:

Tuesday, September 04, 2003

10

QA CHK:

A2

GSM/DCS (INGELA)

DOC CTRL CHK:

Date Changed:

Size:

TITLE:

12 1 8 A

U8100 PT V1.3 Staggered AMD

MFG ENGR CHK: Changed by: JS Joo

H

LG ELECTRONICS INC.

JS Joo

REV:

Drawing Number:

Page:

7:25:06 pm

4

11

12

9. CIRCUIT DIAGRAM

2

4

3

5

6

7

8

9

10

12

11

DCIN_3

1

A

A

R3378 3.3K E

Q3203 DTA114EETL

VDIG B C

0.1u

100K

R2101

VBATI

C2281

4.7u C3013

4.7u

C2211

C2212

0.1u

0.1u

C2213 C2214 0.1u 0.1u

R2220

M12 A3

100K

R3026

R2212

E1

0

C3246

LM20BIM7X

V+

VO

3

C7 M10 L10 K10 L11 K11 J11 J10 J9 D9

RTEMP

R3384

VLOOP WPOWERSENSE WRFLOOP GPA6 VBACKUP

NA R3396

U3106 NA

B4

0.1u

ADCSTR

0

4

D

A12

0

0

VBAT_C

1 GND2 NC 2 GND1

J12 VREF L5 DEC0 K6 DEC1 K7 DEC2 H12 IREF

R2214 R2215 0.1

DCIN_2

F12

C3271 47p

E VBATI

VBAT

C2607

C3272 47p

NA

24

DACDAT DACSTR DACCLK

R3042 100K

R3043 100K

D4

E10 G12 C12 E12 E11 D11 D12

VSSPA VDDPA VDDBUF PASENSE+ PASENSEPAREG IOUT

F

VBAT_D NBUCK MOD1

SWBUCK VBUCK VDD_IO

N2000 VINCENNE

VDIG

BEARP

FGSENSE+

FGSENSE-

TEST

VSSPA VDDPA_DAC VDDBUF PASENSE+ PASENSEPAREG IOUT

M5

VDDCODEC

0

R3045 100K

R2218

R3046 100K

C2209 0.1u

R3047

M3 C2210 0.1u

R3049

100K

100K

R2217

M9

0 C2207

G

0.1u

DACO1 DACO2 DACO3

TXON EXPOUT FF_IN

K1 PCMSYN J1 PCMCLK K2 PCMO J2 PCMI

PCMSYN PCMCLK PCMDATB PCMDATA

VDD_A

A11

2

VDD_B

C11

C2203 1u

R2235

h lc EXTLDO

M11 L12 L2

VBAT_C

R2202 0 R2203 1K 1608

VDDBEAR

VDDADC

K8 VSSADC K5 VSSCODEC K4 VSSBEAR

A2

1608

R3345 0.51 2125

0

VRTC

A5

BEARN

AUXO1 CCO

MIC1P

MIC1N AUXI1 MIC2P MIC2N AUXI2

GPA5 AUXO2 VSSTH31 VSSTH30 VSSTH29 VSSTH28 VSSTH27 VSSTH26 VSSTH25 VSSTH24 VSSTH23 VSSTH22 VSSTH21 VSSTH20 VSSTH19 VSSTH18 VSSTH17 VSSTH1 VSSTH2 VSSTH3 VSSTH4 VSSTH5 VSSTH6 VSSTH7 VSSTH8 VSSTH9 VSSTH10 VSSTH11 VSSTH12 VSSTH13 VSSTH14 VSSTH15 VSSTH16

A1 B2 C3

R3031 0

B5 G11 H11

A8 G10 F10

M4

S2

2 G1

G2 5

1

D1 6

S1

C2638 C2637

L3

C2619 100u

L4

4

SI1555DL

0.22

L2200

V2201 RB521S-30

M8 L8

M6 M7 L7 L6

K12 J4 E4 F4 G4 H4 J5 J6 J7 J8 H9 G9 F9 E9 D8 D7 D6 F7 G7 G6 E5 E6 E7 E8 F8 G8 H8 H7 H6 H5 G5 F5 D5

C2608 1u 1608

22p C2614

22K R2617

0.068u

WDCDCREF WPAREF VCXOCONT

5

R2614

R2201

R2615

NA

VMEM

C2603 VDIG

D2 C2617 0.068u

D1 D3

C2610 22p

C2 D5

C2609 0.01u

MICN

MICP_INT

ATMS

MICN_INT

ATMS_CAP AFMS_R

ATMS_INT

AFMS_L

ATMS_AD AFMS_L_INT

VDD

R2608

A1

3.9K C2605 0.1u

R2607

C2

VDD

VO2

C2633

IN-

VO1

C 22p

IN+

BYPASS

C3 A3 A2 B2 B3

SD_SEL SD_MODE

GND

L2606

R2621 0

L2605

R2620 0

SPKP SPKM

C2606 0.33u 1608

C2632 22p

LM4898ITL

3.9K

10u 2012

R2609 33K

VCORE

C3274 NA

VDIG

0.22

A2 A1 A3 A4

AMPCTRL

N2603 ADG702 1 6 VDD D 2 5 S NC 3 4 GND IN

D

R2610 100K

SPKMUTE

C2604 0.1u L2603 BLM15BB750SN1J L2608 BLM15BB750SN1J

R2619

0

R2618

0

TP3318

EARP TP3319

EARM

C3221 X2603 SUMY0005601

C2616 22p

C2630 22p

OBG-15S44-C2KU NA

C2631 22p

22p

C3270 NA

R3397

E

0

C2613 0.033u

B4 A5 B5

C3266

C3277 NA 4.7uF, 2012

10p 5 2 3 4 6 1

C3268 47p

TJATTE2

D2016 RB521S-30

33K

B1

0

C3 GND4 C4 GND5 C5 GND6

B1 GND1 B2 GND2 B3 GND3

R2606 N2601

1u

R2213

0.1u

MICP

NA

C1

VBATI

IP4025CX20

D4 AFMS_R_INT C1 CCO

C2615 10 0.068u

C3273

1608

10u 2012

L2202

TXON EXPOUT FF_IN

N2602

AUDIO AMP VBATI

0

BLM18PG121SN1 1608 120 OHM BEAD

C2205

TGBUZZ

NA

NA

C2200

0

2012 C3248

R2613

C2634

NA C2635

4

IO3

NA NA

HOOK C2611 100u

R2210

C2206

VCORE

22p C2618

C2612

22uH

ELL5GM220M CHOKE COIL

10u

L9

FB4

R2200

4.7u

VBACKUP

R2208 0.1u

3 D2

1608

REF1

IO2

X2300 5 P1 P5 6 P2 P6 7 P3 P7 8 P4 P8 9 GND3 GND1 10 GND4 GND2

6

IO4

REF2

3

FB3

0

C2202

BACKUP BATTERY

C3247

Q2200

A4

IO1

R3248

KPD9D-8S-2.54SF

C2312

V2300 DALC208SC6

1

C2303

0

i b

ADSTR

C9 DACDAT B10 DACSTR A10 DACCLK

R3041 100K

PT1 47K 1%

PBUCK

B11 BDATA B3 VIBR

R3382

MOTOR_BATT

0 R3327 180K 1%

VDDBUCK VBAT_C

H10 VSS_A G3 VSS_B C6 VSS_C E3 VSS_D D10 SUB B1 VSSBUCK

2012

R3379

R3328 8.2K 1%

R2306 47

BA3000

VBAT_B

GPA0 GPA1 GPA2 GPA3 GPA4 GPA6 GPA7 GPA12 GPA13

s ip

RB521S-30 R2313

B12

VBAT_A

o M

R2216

0.05

F11

0.05

C2280 NA 1608

VDD_D VDD_E VDDLP

E2 DCIO D1 CHREG D3 CHSENSE+ D2 CHSENSE-

DCIN_3 Q2201 Si5441DC 8 1 D1 D6 2 7 D2 D5 3 6 D3 D4 4 5 G S

VDD_B EXTLDO

100K

R3019 R2205

VDD_A

1 2 3 4 11 12

V3202

R2305 15K

B

SIM HOLDER

22p

VDIG

CDCDB

1608 C2301 1u H3 G1 G2 F3 C2300 NA F2

C2302

K9 MCLK C8 SDA B9 SCL K3 CLK_REQ C10 SLEEP

C

5

SIMDAT SIMCLK SIMRST CDCDA

1u

H1 SDAT J3 SCLK H2 SRST

TP3316 INDICATOR LED

1000p

10K

C2302 & C2303 CLOSER TO SIM SOCKET

B6 L1 C2 F1

1

R2312

VDIG

SIMDAT0 SIMCLK0 SIMRST0

RESOUT0n IRQ0n PWRRSTn

NA R3376 0

A6

2

0

TP2310

LED2 32KHZ SIMOFF SIMVCC

R2107

A9 C1 B8

0

TP2311

LED1

NA

R3002 TP3000

RESETB IRQ PWRRST

INTLCKB

M1 XTAL1 M2 XTAL2

R3294

RTCCLK

VDIG

EN_LED_TC

R2314

C4 ONSWA C5 ONSWB A7 ONSWC B7

MCLK I2CDAT I2CCLK CLKREQ PWRREQn

1SS388

ROP-101-3029_2C

ONSWAn ONSWBn ONSWC

B

EN_LED_R 100K

R2106

D2010 C2621 TP3004

C3269 47p

C3267 NA

X2602

C3278 100p

VDIG

VEXT15

N2203 VDIG 2 C2274 1 0.1u

D2015 R3381 RB521S-30 47K

VSS

F

VOUT NC

3 C2272 4 1u 1608

S-817A15ANB-CUE-T2

R3385 NA R3395

VIN

GPA6

0 C3275 NA

R3303 100K

R3386 NA

1.5V REGULATOR

3.3V REG C2276 100p

N2204

PWRRSTn

3 2

VBUS

1

ON_OFF BYPASS

GPIO05

VIN

VOUT

IRDA_REG_CTRL

VBATI

3 2

5

LP2985IM5X-3.3

USBSENSE

100K

C2277 4.7u

1

R2232 10K

R3051

C2278 2.2u 2012

C3046 100p

N3000

VUSB

4

GND

C3051 2.2u 2012

ON_OFF BYPASS

G

4 VIRDA

GND VIN

VOUT

LP2985IM5X-2.8

R3050 0 5 C3052 4.7u

R2233 51K

IRDA REGULATOR

USB REGULATOR H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP 1

TAE-SUNG, HA

TITLE:

DOC CTRL CHK: MFG ENGR CHK: Changed by: mentor

1

2

3

4

5

6

7

- 239 -

8

9

Date Changed:

Time Changed:

Tuesday, September 04, 2003

10

QA CHK:

H

LG ELECTRONICS INC.

TAE-SUNG, HA

Drawn by: R&D CHK:

REV:

Size: A2 BB MAIN PCB 12 1 8 A VINCENNE U8100 PT V1.3 Staggered AMD

Drawing Number:

Page: 5

7:25:29 pm

11

12

9. CIRCUIT DIAGRAM

1

3

2

6

5

4

7

8

9

10

11

12

* MEMORY CHANGE HISTORY

U8100 WS01-5

ADDRESS X DATA = 2^23 X 2^4 = 2^27 = 128MBIT A22 = 128MBIT, A21 = 64MBIT

0

R2237

R3103

0

TP3100 DAT(0:15)

100

DAT(11) DAT(10)

K20 E1 J21 AA11 Y12 AA13 R14

ADR(19) ADR(20) ADR(21) ADR(22) ADR(23)

ADR(24)

DAT(0:15)

DAT(0) DAT(1) DAT(2) DAT(3) DAT(4) DAT(5)

DAT(9)

DAT(10) DAT(11)

GND

7 C3137

IrDA

VCC

6 0.47u

SHIELD TXD LEDK LEDA

1608

KEY I/F

H3 C6

MEM_OE_N MEM_WE_N

D4 C4

R3323

100K

MEM_BE1_N MEM_BE0_N

2

ADR(15) ADR(14) ADR(13) ADR(12) ADR(11) ADR(10) ADR(9) ADR(8) ADR(7) ADR(6) ADR(5) ADR(4) ADR(3) ADR(2) ADR(1)

VMEM

C

VCCS

J6

_OE _WE G3 VSS1 J9 VSS2 L4 VSS3

ACC _UB _LB

C3133

C3135 C3134

0.1u

0.1u

0.1u

D

VPPFLASH V2203

DAT(13) DAT(14) DAT(15)

NA

NA

ADR(1:24)

1K

MEM_WAIT_N

E ADDRESS X DATA = 2^23 X 2^4 = 2^27 = 128MBIT A22 = 128MBIT

Rout track on inner layer

LCD I/F

DAT(0:15)

VDIG J7 H6 J6 H5 J4 H4 J3 H3 G6 K6 G5 K5 K4 G4 K3 G3

DAT(15) DAT(14) DAT(13) DAT(12) DAT(11) DAT(10) DAT(9)

I2CDAT CIPCLK CIVSYNC CIHSYNC CIRES_N CID0 CID1 CID2 CID3 CID4 CID5 CID6 CID7

DAT(8) DAT(7) DAT(6) DAT(5) DAT(4)

VMEM

DAT(3) DAT(2) DAT(1)

VDIG

CS2

NA

DAT(0)

CAMERA I/F

1

TP3344

ADR(24)

VMEM

A1 A2 A7 A8 B1 B2 B7 B8 C1 C8 E8 H7

LCDRESX LCDCSX_SUB LCDWRX LCDRS LCDCSX_MAIN LCDRDX PDID0 PDID1 PDID2 PDID3 PDID4 PDID5 PDID6 PDID7

R3321

D19 C19 D18 C20 C21 E18 B18 D17 C18 B19 A20 H13 G14 B20 Y2 W3 H18 H15 G21 E19 E20 E21 H14 F19 F20 G18 G19 G20

MEM_CS0_N MEM_CS1_N MEM_CS2_N MEM_CS3_N MEM_WE_N MEM_OE_N MEM_BE0_N MEM_BE1_N MEM_ADV_N MEM_CLK

R3319

J8 H7 B10 D9 C8 D8 C1 D3 B9 G8 D2

U3104 AM29BDS128HD9VKI

FLASH H2

MEM_CS2_N

MEM_WAIT_N MEM_ADV_N MEM_CLK MEM_OE_N MEM_WE_N

ADR(23) ADR(22) ADR(21) ADR(20) ADR(19) ADR(18) ADR(17) ADR(16) ADR(15) ADR(14) ADR(13) ADR(12)

F

ADR(11) ADR(10) ADR(9) ADR(8) ADR(7) ADR(6) ADR(5) ADR(4) ADR(3)

VMEM

ADR(2) ADR(1)

D1 VCC1 J5 VCC2 F8 VIO1 H1 VIO2

J2 _OE C5 _WE

G8 VSS1 J1 VSS2 K2 VSS3 K7 VSS4

ACC

C3225 0.22u

I2CCLK_CAMERA

ADR(1:24) D8 E5 F4 F5 E4 D3 G7 F7 E7 C7 D7 F6 E6 C6 D6 C3 E3 F3 D2 C2 E2 F2 G2

C4 RDY G1 _AVD E1 CLK

D4

R3333 NA

A22 A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

_CE

D5 _RESET F1 _WP

RESOUT0n

I2CCLK

DQ15 DQ14 DQ13 DQ12 DQ11 DQ10 DQ9 DQ8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0

50V 1608

G C3276

C3222

0.1u

0.1u

PCM I/F VPPFLASH

1

Engineer:

3G HANDSETS LAB DEVELOPMENT GROUP1

SUNG-JU, YOU

R&D CHK:

LOW POWER MODE : LEDA VCC

TITLE:

DOC CTRL CHK: MFG ENGR CHK: Changed by: mentor

4

5

6

7

- 240 -

8

9

Time Changed:

Date Changed: Tuesday, September 04, 2003

10

REV:

QA CHK:

H

LG ELECTRONICS INC.

SUNG-JU, YOU

Drawn by:

SIR TRANCEIVER

3

ADR(17) ADR(16)

J5 VCCF1 L5 VCCF2

RDY _ADV CLK

SD(L:ACTIVE, H:SHUTDOWN)

2

B

ADR(18)

_RESET _WP

H

1

ADR(22)

ADR(20) ADR(19)

RB521S-30

4 3

ADR(23)

ADR(21)

27

8

5

R3346

SD RXD

E5 B2 B4

MEM_WAIT_N MEM_ADV_N MEM_CLK

F9 E9 E6 D7 E4 F4 G9 D9 F8 E8 D8 C8 F7 E7 C7 C3 D3 E3 F3 D2 E2 F2 G2

DAT(12)

R2303 470 VIRDA

N3100 CIM-80S7B-T

D5 C5

C2 C3136 0.22u 50V 1608

DAT(8)

VCORE

RTC_GND

RESOUT0n

MCP

_CE1S CE2S_ZZ

ADR(1:24) A22 A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

DAT(7)

VDIG

R2622

MARITATCK MARITATMS MARITATDI MARITATDO MARITATRST MARITARTCK MARITATEMU0 MARITATEMU1

J2 D6

_CEF1 _CEF2

VMEM

DAT(6)

TP3115 TP3116

A7 B7 C7 D7 C6 B5 C5 D6 B4 C4 D5 B3 D4 C3 B2 A1

R3320

PDIRES_N PDIC0 PDIC1 PDIC2 PDIC3 PDIC4 PDID0 PDID1 PDID2 PDID3 PDID4 PDID5 PDID6 PDID7 I2CSCL I2CSDA CIPCLK CIVSYNC CIHSYNC CIRES_N CID0 CID1 CID2 CID3 CID4 CID5 CID6 CID7

ADR(18)

MEM_CS3_N

U3103 S71WS256HC0BAW00

H9 K2 K6 K9 L2 L3 L6 L7 L8 L9

ADR(17)

NA

ADR(16)

R3338

ADR(15)

100K P_MODE

ADR(14)

TP3117 TP3118

VDDMC VDDDM VDDUSB VDDRTC VDDA0 VDDA1 VDDA2

AA19 N1 R12 Y14 M20 D20 B12 R1 Y1 AA7 H20 A15 L21 A17 B1 K2 A9 B6 R20 M2 N2 Y10 C2 B16 A13 A11 B8 A5 A3 H2 U1 AA1 AA3 Y6 Y18 V20 N21 B21 A19 VDDC00 VDDC01 VDDC02 VDDC03 VDDC04 VDDC05 VDDC06 VDDC07 VDDC08 VDDC09 VDDC10 VDDC11 VDDC12 VDDC13 VDDC14 VDDC15 VDDC16 VDDC17 VDDC18 VDDE00 VDDE01 VDDE02 VDDE101 VDDE102 VDDE104 VDDE106 VDDE108 VDDE110 VDDE112 VDDE200 VDDE201 VDDE202 VDDE203 VDDE204 VDDE205 VDDE206 VDDE207 VDDE208 VDDE209

E2 J7 F3 F2 K4 K3 L7 G3 G2 K8 H4 G1 H3 K7 J2 J4 J3 J1 L8 R3126

R2121 NA

JTAG I/F

R2122 3.3K

W8 R10 Y9 AA9 V9 Y8 P11 V10 P20 P19 M15 L19 J14 J19 K19 K14 K15 N18 N19 N20 M19 L15 M18 P14 AA17 Y17 W17 V16 W18 AA15 Y15 W15 V15 W16 V3 W1 W2 V4 R13 V13 W14 Y13

TP2401 TP2402 TP2403

NC0 NC

ADR(13)

H2 B5

MEM_CS0_N MEM_CS1_N

R3337

L14 E5

TP2404 TP2405

HSSLRXCLK HSSLRX HSSLTXCLK HSSLTX

CS0_N CS1_N CS2_N CS3_N WE_N OE_N MEMBE0_N MEMBE1_N MEMADV_N MEMCLK MEMWAIT_N

KEYOUT0 KEYOUT1 KEYOUT2 KEYOUT3 KEYOUT4 KEYOUT5 KEYIN0 KEYIN1 KEYIN2 KEYIN3 KEYIN4 PCMCLK PCMSYN PCMDATA PCMDATB

HSSL

USBDP USBDM USBPUEN

ADR(12)

DAT(1) DAT(0)

DQ15 DQ14 DQ13 DQ12 DQ11 DQ10 DQ9 DQ8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0

100K for Intel

N3 N8 N4 N7

HSSLRXCLK HSSLRX HSSLTXCLK HSSLTX

ADR(11)

DAT(3) DAT(2)

CS 0,1,3

100K

J15 J20 H19

USBDP USBDM USBPUEN

USB

o M

DACCLK DACDAT DACSTR ADCSTR

ADR(10)

DAT(4)

VMEM

R3322

P3 P2 P4 P7

DACCLK DACDAT DACSTR ADCSTR

DAC

ADR(9)

DAT(5)

3.3K

1SS388

ADR(8)

DAT(7) DAT(6)

Q3202 PMST3904

D2012

ADR(7)

R2304

USBSENSE BL_EN FOLDER_DET EN_LED_R EN_LED_G EN_LED_B IRDA_REG_CTRL

ADR(6)

3.3K R3330

LCDVSYNCI SPKMUTE

E

ADR(5)

h lc D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

i b

MARITA

ADR(4)

2

KEY_LED_ONOFF

D2000 ROP-101-3035_1

100K

NA

CAM_FLASH_SHOT

PULSESKIP

ADR(3)

3

TP2125

ADR(2)

TP3111 TP3112 TP3113 TP3114

UARTRX1 UARTTX1 UARTRTS1 UARTCTS1 CAM_REG_EN CAM_FLASH_ON

UART1 VDIG

GPIO00 GPIO01 GPIO02 GPIO03 GPIO04 GPIO05 GPIO06 GPIO07 GPIO10 GPIO11 GPIO12 GPIO13 GPIO14 GPIO15 GPIO16 GPIO17 GPIO20 GPIO21 GPIO22 GPIO23 GPIO24 GPIO25 GPIO26 GPIO27 GPIO30 GPIO31 GPIO32 GPIO33 GPIO34 GPIO35 GPIO36 GPIO37 GPIO40 GPIO41 GPIO42 GPIO43 GPIO44 GPIO45 GPIO46 GPIO47

s ip

ADR(1)

4.7K

CAMERA_DET GPIO05 AMPCTRL TGBUZZ UARTRX0 UARTTX0

ISSYNC_N ISEVENT_N IRQ0_N

DAT(8)

ADR(1:24) C17 B17 G13 C16 C15 B15 H12 D14 B14 C14 G12 B13 C13 H11 D12 C12 G11 D11 C11 H10 C10 D10 H9 C9

4.7K R3329

M14 P18 R21 R8 P9 AA2 Y3 W4 V5 Y4 V6 W5 Y5 AA5 W6 V7 W7 Y7 P10 P15 N14 W20 V19 W21 U18 T18 U19 U20 N15 U21 T19 T20 R19 R18 V17 AA21 Y19 AA20 W19 Y20

BL_PWL 7C_LED_VDD_EN

IRQ0n

H8 K8 H7 J7 K5 J4 H4 K3 J8 G7 K7 H6 H5 K4 G4 J3

DAT(15)

NC1 NC2 NC3 NC4 NC5 NC6 NC7 NC8 NC9 NC10 NC11 NC12

R2222

0

0

0

0 0

Rout track on inner layer

0.1u C2261

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A24

A

NC13 NC14 NC15 NC16 NC17 NC18 NC19 NC20 NC21 NC22 NC23 NC24

R3110

R3325

0.8 PITCH 9 X 12 X 1.4 0.8 PITCH 9 X 12 X 1.4

DAT(12)

SIMDAT0 SIMRST0 SIMCLK0

100K

R2102

0.1u C2259

VSSMC VSSDM VSSUSB VSSRTC VSSA0 VSSA1 VSSA2

M3 M4 V2

MCLK SYSCLK0 SYSCLK1 SYSCLK2 SERVICE_N RESPOW_N RESOUT0_N RESOUT1_N RESOUT2_N RESOUT3_N RESOUT4_N CLKREQ PWRREQ_N

100K

130K

R2105

PWRREQn

P13 R3 T2 T3 L3 R2 F4 L1 P8 U2 U3 M8 T4

R3127

100K

R2104

TP2102

UART0

R2301

0.1u C2251

0.1u C2258

0.1u C2260

K18 E3 J18 R11 V12 W13 V14

47

RESOUT0n RESOUT1n

TP3313

G

0.1u C2263

VSSE00 VSSE01 VSSE02 VSSE100 VSSE102 VSSE104 VSSE106 VSSE108 VSSE110 VSSE112 VSSE200 VSSE201 VSSE202 VSSE203 VSSE204 VSSE205 VSSE206 VSSE207 VSSE208 VSSE209 VSSE210 VSSE211

330p

ISSYNCn ISEVENTn

F

0.1u C2219

128/128/64 128

.8 PITCH 9 X 12 X 1.25 0.8 PITCH 9 X 11.5 X 1.0

0.1u C2262

0.1u C2252

L4 M7 W9 E4 D15 D13 G10 G9 H8 A2 G4 R4 U4 R9 V8 Y16 V18 Y21 F18 A21 D16 L18

C2102

R2109

RESOUT3n

D

0.1u C2253

0.1u C2257

0.8 PITCH 9 X 12 X 1.4 0.8 PITCH 9 X 12 X 1.4

128/128/64 0 128

NA

0 TP2101

PWRRSTn

CLKREQ

0.1u C2245

0.1u C2250

0.1u C2255 0.1u C2256

0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4

128/128/64 128

DAT(14)

DIRMOD0 DIRMOD1 DIRMOD2 DIRMOD3 DCLK IDATA QDATA TXON RXON RFCLK RFSTR RFDAT BANDSEL0 BANDSEL1 ANTSW0 ANTSW1 ANTSW2 ANTSW3 PCTL

TP2100

MCLK TP3126

SYSCLK1 SYSCLK2

C2104 1000p

0.1u C2242

0.1u C2247

0.1u C2246

64/64/16 64/64/16

0.8 PITCH 9 X 12 X 1.4 0.8 PITCH 9 X 12 X 1.4

128/128/64 128

U8100 PT V1.1 Staggered AMD

DAT(9)

W10 RTCBDIS_N V11 RTCIN W11 RTCOUT P12 RTCDCON W12 RTCCLK

R3100 NA Q2100 RN1107

E

C

0.1u C2216

0.1u C2244

0.1u C2243

TCK TMS TDI TDO TRST_N RTCK TEMU0_N TEMU1_N IRRX IRTX IRCTRL MMCCLK MMCCMD MMCDAT MSSCLK MSBS MSSDIO SIMDAT0 SIMRST0_N SIMCLK0 SIMDAT1 SIMRST1_N SIMCLK1 KEYOUT0_N KEYOUT1_N KEYOUT2_N KEYOUT3_N KEYOUT4_N KEYOUT5_N KEYIN0_N KEYIN1_N KEYIN2_N KEYIN3_N KEYIN4_N PCMCLK PCMSYN PCMDATA PCMDATB TSYP TSYM TSXP TSXM

B

0.1u C2217

0.1u C2223

0.1u C2222

0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4

RTC_GND

TP2106

120K

0.1u C2220

64/64/16 64/64/16 64D/64D/16PS 128L/128L

DAT(13)

B

R2123

R2403

22p

TP3317

VPPFLASH

U8100 ES01-3 TOSHIBA 0.1u C2221

0.1u C2218

C2101

R2238

MODA MODB MODC MODD DCLK IDATA QDATA TXON RXON RADCLK RADSTR RADDAT BSEL0 GPRFCTRL ANTSW0 ANTSW1 ANTSW2 ANTSW3 PCTL 1 2

22p

4 MC-146 B2100

32.768KHz

C2100

3

C2100 and C2101 close to B2100

C

OPTION U8100 ES01-2

ONSWC

32.768KHz

R2221

47

R2241

RF I/F

R2100

RTCCLK

R2223

U8100 ES01-1 DEFAULT

OPTION U8100 PT V1.0 NMBI TOSHIBA U8100 PT V1.0 Staggered TOSHIBA

TP3103

1.5V

1.5V

VRTC VEXT15

TP3102

3.3V VUSB

NC3 NC4

VMEM

M1 M10

1.8V

VDIG

0.8 PITCH 9 X 12 X 1.4 0.8 PITCH 9 X 12 X 1.4 0.8 PITCH 9 X 12 X 1.4

TP3101

2.75V

128/128/64 128 128/128

A1 A10 B3 B6 B7 B8 B9 C9 F5 F6 G5 G6 G8

1.8V

VCORE VMEM

U8100 ES01-6 TOSHIBA

H8 J8 K1 K8 L1 L2 L7 L8 M1 M2 M7 M8

VDDE 1.5V

VCORE

0.8 PITCH 14 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4 0.8 PITCH 10 X 8 X 1.4

NC1 NC2 RFU1 RFU2 RFU3 RFU4 RFU5 RFU6 RFU7 RFU8 RFU9 RFU10 RFU11

VDDC 1.5V VDDC 1.5V VEXT15

A

MCP 64/08. 64/64/16 64/64/16 64/64/16 64/64/16 64/64/16 64/64/16

RFU12 RFU13 RFU14 RFU15 RFU16 RFU17 RFU18 RFU19 RFU20 RFU21

U8100 WS01-1 U8100 WS01-2 U8100 WS01-3 U8100 WS01-4 2002.09.13

Size: A2 BB MAIN PCB 12 1 8 A MARITA U8100 PT V1.3 Staggered AMD

Page:

Drawing Number:

9:42:54 am

6

11

12

9. CIRCUIT DIAGRAM

1

2

4

3

6

5

7

9

8

12

11

10

VBATI

SC600B VCAM

7C_LED_VDD

AXK7L80225

7C_LED_VDD CAM_FLASH_ON CAM_FLASH_SHOT

R3388

R3263

0

4.7

1 2 3

G3

G4

10

11

FB2

9

12

1608

8

13

CID4 BL_PWL FOLDER_DET

4

CID5

KEY_LED-

R3357

CIVSYNC

51

R3364

EARM EARP BL_EN MOTOR_BATT SPKP SPKM

14

7 R3360

CIPCLK

51

6

15

5

16

R3366

17

R3367

3

18

2

19

1

20

G1

G2

51

C3201 1u 1608

6

R3389

100

R3390

100

7C_LED_VDD_EN B

EN_LED_TC

C3260

C3259

20p

12

EMX18 Q3200

NA

NA

R3210 3

4

NA

A1 A2 A3 A4 A5 B1 B5

2 1

NA

R3252

VBACKUP

TP3338 TP3339 TP3343 TP3340

PCMCLK

PDM : ENEY0003301 GT059-24P-3BL-P800

PCMSYN

HF MIC

TP3202

PCMDATA

NA 0 NA

R3220 R3249 R3222

R3223

0

R3225

NA

R3227 R3228

0 0

X3203 25 VBAT_GND_1 26 VBAT_GND_2 1 BATT_ID 2 HF_MODE 3 DSR 4 PWR_+5V_1 5 PWR_+5V_2 6 ON_SW1 7 PCM_RXA_IN 8 PCM_CLK 9 PCM_SYNC 10 USB_RX 11 PCM_TXA_OUT 12 PWR_GND_1 13 RXD 14 TXD 15 USB_TX 16 USB_PWR 17 DCD 18 RI_TMS 19 PWR_GND_2 20 RFR_RTS 21 PWR_+4_2V_1 22 PWR_+4_2V_2 23 CTS 24 DTR TP3307 27 V_BAT_1 5V 28 V_BAT_2 29 V_BAT_3 30 GND1 31 GND2

100K

DTMS_e DFMS_e CTMS_e CFMS_e VPPFLASH_e CTS_ON_e DCIO_e

BLM18PG121SN1 L2201

HF SPK N TP3203 Q2300 RN1107

HF SPK P TP3204

C3220 0.1u

0 V2500

UARTRTS1

RB521S-30 NA R3206

UARTRX1

NA

PCMDATB

R3229 R3230

0 0

R2319

1K

R3232 R3233

0 NA

NA

R2503

R2500

R3237

C3215 0

R3341

NA

G R3235 NA

2.75V

C2208

33u

1u

3216

1608

2

H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP1

S .Y SEOK

R&D CHK:

TITLE:

DOC CTRL CHK: MFG ENGR CHK: Changed by: mentor

4

5

7

6

- 241 -

8

9

Date Changed:

Time Changed:

Tuesday, September 04, 2003

10

QA CHK:

H

LG ELECTRONICS INC.

S .Y SEOK

Drawn by:

I/O CONNECTOR

3

DTC SENSE TP3205

1

3

4

D2

5 D4

6 D5

D3 GND

USB FILTER

SMF05C

SP3205 SP3200 SP3206 SP3207 SP3201 SP3208 SP3202 SP3209 SP3203 SP3210 SP3211 SP3204 SP3212

UARTTX1

D1

100K 0.1u 0.1u 0.01u

C3212 1000p C3213 1000p C3219 1000p

NA

R3398 C2304 C2500 C2279

R2504

R2501

NA

USBUF01W6

CRS08 V3200

V3201

L2500 1 6 D1 D4 5 2 3_3V GND 3 4 D2 D3

F

0

VBAT

USBPUEN

CAMERA ROTATION DETECTOR

3

KEYPAD BACKLIGHT BLUE LED I/F

5

IP4022CX20

DTMS_i DFMS_i CTMS_i CFMS_i VPPFLASH_i CTS_ON_i DCIO_i

VBATI

USBDM

2

CURRENT LIMIT 15mA x 16 = 240mA

UMC4N

C B

VCAM

C3205 10p

1

C

12

R2502

USBDP

4

E

NA NA NA NA

R3347

D2 D3 C3 D4 TP3337 D5 TP3336 D1 C5

UARTRX1 UARTTX1 UARTRX0 UARTTX0 VPPFLASH ONSWBn DCIN_3

VBUS

CAMERA_DET

5

VDIG

N2300

TP3306

100K

6

R3208

NA

R3211 R3353 R3352 R3351 R3350

KEY_LED_ONOFF R3207

R3209

C3261

C3258

20p

C3

20p

C1

ESD4

20p

A3

ESD3

KEY_LED-

Q3201

TP3200

E

2

D2014 1SS388

SUB LCD BACKLIGHT 4.5V

HF DETECTION

VBAT

R2505

CSPESD304

A1

ESD2

C3 ESD4

B2

GND

C1 ESD3

ESD1

A3 ESD2

CSPESD304 D2018

A1 ESD1

C3

B2

GND

C1

ESD4

D2009

A3

ESD3

CSPESD304

A1

ESD2

C3 ESD4

B2

GND

C1 ESD3

ESD1

A3 ESD2

CSPESD304 D2008

A1 ESD1

GND

D2007

C3252

o M UARTCTS1

1

D2013 1SS388

NA

CAMERA REGULATOR

N3200 A3212ELH 1 VDD 3 GND OUT 2

EN

VDIG

DCIN_2

C4

300K

R3331

C3245 10u

F

C3204 0.1u

FID1

9 8 7

D

KNATTE

VCC

R3332

240K

VCAM

100K

R3344

51

h lc

i b

TP3342 TP3341

G

CF2-

CID6

C3249 20p

20p

C3255

VBATI

C3243 470p

FID0

10

1608

51

I2CDAT

R3363

CAMERA I/F

E

MIC5219BM5

GND

CID7

B'd to B'd CONNECTOR I/F

C3244 2.2u

CF1-

VIN

CIHSYNC

CID3

MARITATEMU1 MARITATEMU0 MARITARTCK MARITATRST MARITATDO MARITATDI MARITATMS MARITATCK

2012

CF2+

CF1+

FB1

CID0

SYSCLK1

EN_LED_R EN_LED_G EN_LED_B KEYOUT0 KEYOUT1 KEYOUT2 KEYOUT3 KEYOUT4 KEYOUT5

CAM_REG_EN

s ip

SC600BIMSTR

VOUT

CHARGE PUMP

51

R3365

N3201

C3203 1u 1608

CIRES_N

4

U3102 1 5 IN OUT 2 GND 3 4 EN ADJ

C3202 10u 2012

I2CCLK_CAMERA

CID2

LCDCSX_SUB LCDRESX LCDVSYNCI LCDWRX LCDRS LCDCSX_MAIN LCDRDX PDID0 PDID1 PDID2 PDID3 PDID4 PDID5 PDID6 PDID7

5

51

CID1

GND5 C2 GND4 C1 GND3 B4 GND2 B3 GND1 B2

D

1u 1608

X3201 PDM : ENBY0017602

B2

C

C3200

ONSWAn KEYIN0 KEYIN1 KEYIN2 KEYIN3 KEYIN4

20p

B

A

VBATI

2.7K

VDIG CONN_10_5087_060_920_829 X3200 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62

R3236

A

REV:

Size: A2 BB MAIN PCB MULTIMEDIA INTERFACE 12 1 8 A U8100 PT V1.3 Staggered AMD

Drawing Number:

Page:

2:11:39 pm

7

11

12

9. CIRCUIT DIAGRAM

1

2

3

5

4

6

7

9

8

10

11

12

A

A 1.5V

1.5V

1.5V

VEXT15 WANDAVDDA

1.5V

VCORE WANDAVDDD

0

0

R2224

R2236

VCORE VRTC VEXT15

VCORE

B

B C2227 0.1u

C2229 0.1u

s ip

C2238 0.1u

C2234 0.1u

C2236 0.1u

C2241 0.1u

C2240 0.1u

C2239 0.1u

C2230 0.1u

C2232 0.1u

B1 D2 G1 K2 M1 R1 T2 U5 R13 U16 R16 N17 K17 H17 F17 D16 A17 B14 A12 B8 A6 A3 L15 R12 T17 U6 U10 R11 JTAG_TRSTN JTAG_TCK JTAG_TMS JTAG_TDI JTAG_TDO EMU1 EMU0

VDD21 VDD20 VDD19 VDD18 VDD17 VDD16 VDD15 VDD14 VDD13 VDD12 VDD11 VDD10 VDD9 VDD8 VDD7 VDD6 VDD5 VDD4 VDD3 VDD2 VDD1 VDD0 VDD_DPLL VDDA_CS_APLL VDD_CLK32 VDDA_TX VDDA_RX VDDA_BG

G16 G17 G15 F16 G13 E15 F13

47p

i b

RXIA RXIB RXQA RXQB C2400

ADCSTR

HSSL LINK (MARITA)

B16 HSSLRX_D A16 HSSLTX_CLK A15 HSSLTX_D C14 HSSLRX_CLK

HSSLTX HSSLRXCLK HSSLRX HSSLTXCLK

D4 ID_BALL A13 IS_SYNC_N B12 IS_EVENT_N U12 APLL_ATEST1

ISSYNCn ISEVENTn

CLK INTERFACE

C2103 330p

MCLK RTCCLK CLKREQ RESOUT1n

VINCENNE INTERFACE

E12 UART_TX C13 UART_RX

U11

TP2116

D2006

ROP-101-3033_1

C2235 0.1u

C2228 0.1u

C2225 0.1u

C

C2 C1 F5 E3 G5 E1 F2 F1 G3 G2 H5 H1 H2 J2 J3 J5 K3 K5 K1 L1 L3 M2 L5 N1 M3 M5 P2 P3 R2 T1 N5 U1

D

E

U3 EMIF_AWE_N T3 EMIF_ARE_N U2 EMIF_AREADY

U13 MCLK T16 CLK32 R15 HCLK T15 CLKRQ N13 RESET_N

N15 DAC_CLK L13 DAC_DAT M15 DAC_STR

DACCLK DACDAT DACSTR TP2119

F

o M N8 DAC_I_OUT U8 DAC_I_OUT_INV U7 DAC_Q_OUT R7 DAC_Q_OUT_INV T7 DAC_TXEXTRES

TXIA TXIB TXQA TXQB

N12 EXT_MEM_UBUS10 T14 EXT_MEM_UBUS11 R14 EXT_MEM_UBUS12 E17 EXT_FRAME_STROBE

VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 VSS22 VSS23 VSS24 VSSA_CS_APLL VSSA_RX VSSA_TX VSSA_BG

E

ADC_I_IN ADC_I_IN_INV ADC_Q_IN ADC_Q_IN_INV ADC_RXEXTREF_P ADC_RXEXTREF_N AD_STR

EMIF_D0 EMIF_D1 EMIF_D2 EMIF_D3 EMIF_D4 EMIF_D5 EMIF_D6 EMIF_D7 EMIF_D8 EMIF_D9 EMIF_D10 EMIF_D11 EMIF_D12 EMIF_D13 EMIF_D14 EMIF_D15 EMIF_D16 EMIF_D17 EMIF_D18 EMIF_D19 EMIF_D20 EMIF_D21 EMIF_D22 EMIF_D23 EMIF_D24 EMIF_D25 EMIF_D26 EMIF_D27 EMIF_D28 EMIF_D29 EMIF_D30 EMIF_D31

C2226 0.1u

C2231 0.1u

C2237 0.1u

N6 CPU_IACK R5 CPU_XF N7 CPU_IRQ1 R6 CPU_IRQ0 M17 CPU_CLKOUT

F TP2120

D3 F3 H3 L2 N3 R3 R4 T4 U15 U17 P16 L16 J16 H16 F15 C16 B15 C12 B11 B10 B7 C5 C3 T6 T12 N11 T8 R8 T11

RF TX DATA

R10 N10 R9 T9 T10 N9 0.1u M16

GPO0 GPO1 GPO2 GPO3 GPO4 GPO5 GPO6 GPO7

NA

R17 RADIO_CLK P15 RADIO_DAT M13 RADIO_STR

WCLK WDAT

C17 BOOTMODE0 B17 BOOTMODE1 E13 BOOTMODE2 C15 BOOTMODE3

RF RX DATA

PMST3904

BG_REF

R3326

D15 TESTMODE E11 ANALOG_ENABLE C11 APLL_BYPASS A11 CS_BYPASS

WSTR

1

3

Q3204

RF CONTROL

2

D

L17 K13 K15 K16 J15 J13 H15 H13

C3265

3.3K

R3380

VCORE

2.7K

R3383

VDIG

B2 EMIF_A23 E5 EMIF_A22 A1 EMIF_A21 A2 EMIF_A20 B3 EMIF_A19 C4 EMIF_A18 B4 EMIF_A17 E6 EMIF_A16 C6 EMIF_A15 A5 EMIF_A14 E7 EMIF_A13 B6 EMIF_A12 C7 EMIF_A11 A7 EMIF_A10 A8 EMIF_A9 E8 EMIF_A8 C8 EMIF_A7 E9 EMIF_A6 C9 EMIF_A5 B9 EMIF_A4 C10 EMIF_A3 A10 EMIF_A2 E10 EMIF_A1

h lc

100K

R2402

C

100K

R2401

C2224 0.1u

C2233 0.1u

1%

TP2117

TP2321

TP2320

TP2322

G

R2120 NA

TP2118

C2215 0.1u

R2400 43K

G

H

Engineer:

3G HANDSETS LAB. DEVELOPMENT GROUP 1

MYUNG-LAE, CHO

TITLE:

DOC CTRL CHK: MFG ENGR CHK: Changed by: mentor

1

2

3

4

5

7

6

- 242 -

8

9

Date Changed:

Time Changed:

Tuesday, September 04, 2003

10

QA CHK:

H

LG ELECTRONICS INC.

MYUNG-LAE, CHO

Drawn by: R&D CHK:

REV:

Size: A2 BB MAIN PCB 12 1 8 A WANDA U8100 PT V1.3 Staggered AMD

Drawing Number:

Page:

9:42:54 am

8

11

12

9. CIRCUIT DIAGRAM

1

2

3

4

8

10

9

12

11

A A

LCDRESX NA

LCDVSYNCI LCDWRX LCDRS LCDCSX_MAIN LCDRDX PDID0 PDID1 PDID2 PDID3 PDID4 PDID5 PDID6 PDID7

R1145 R1140 R1141 R1142 R1143 R1144

LCDCSX_MAIN LCDRESX LCDVSYNCI LCDCSX_SUB LCDRS LCDRDX

100 100 100 100 100 100 C35

C36 C37

30p 30p 30p

EN_LED_R EN_LED_G EN_LED_B KEYOUT0 KEYOUT1 KEYOUT2 KEYOUT3 KEYOUT4 KEYOUT5

R1146 R1147 R1148 R1149 R1150 R1153

PDID6 PDID4 PDID2 PDID0 BL_EN EN_LED_G

C44 C45

30p 30p 30p

C46 C41

i b

C42

30p 30p 47p

5

3

4

6 D5

D4

D3

D2

1

SPKM SPKP MOTOR_BATT CAM_FLASH_SHOT

2

D2

NA SMF05C

o M TOSHIBA LCD I/F

BOARD TO BOARD CONECTOR E

U8100 KEY V0.8

2003.11.18

LCDRESX PULL DOWN R MOVE TVS VDIG

U8100 KEY PT V1.1

2004.01.14 ESD EMI FILTER -> RC Filter

F

VBATI_4.2V

KEYIN4

KEYIN3

KEYIN2

KEYIN1 KB2

2

C23 C24 C22 470p 470p 470p

4

7

KB7

KB12

KB17

5

8

0

KB8

KB13

KB18

6

9

#

KB9

KB14

KB19

KB21

KB16

TVS1

R1104 470

KB11

KEYOUT0

470

SIDE3

KB6

B

470

INSTPAR

s ip 1

h lc

C40

30p 30p 30p

100 100 100 100 100 270 C43

MARITATEMU1 MARITATEMU0 MARITARTCK MARITATRST MARITATDO MARITATDI MARITATMS MARITATCK

C38 C39

KB1

R1154

UCLAMP0501H

TVS2

LCDCSX_SUB

END

VA1

C34

30p 30p 30p

470 R1102

VA2

C32 C33

CN964 1 2 3 4

R1103

SIDE2

VA3

C30 C31

30p 30p 30p

D1 1SS388

AVL14K02200

C29

U8100_SIDEKEY_PAD SIDE1

KB26

AVL14K02200

EARM EARP BL_EN MOTOR_BATT SPKP SPKM

100 100 100 100 100 0

AVL14K02200

R1134 R1135 R1136 R1137 R1138 R1139

BL_PWL PDID1 PDID3 PDID5 PDID7 LCDWRX

KEY_LED-

INSTPAR

BL_PWL FOLDER_DET

UCLAMP0501H

40 39 38 VBATI_4.2V 37 36 35 34 33 32 31 30 29 28 VDIG_2.8V 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 7C_LED_VDD 10 9 8 7 6 5 4 3 2 1 CN963

C28

47p 47p

KEYIN0

CONN_40_AXK840145J

270 270

C27

GND

D

R1152 R1151

CAM_FLASH_ON CAM_FLASH_SHOT

D1

C

CAM_FLASH_ON EARP EARM EN_LED_R EN_LED_B

R1097

B

ONSWAn KEYIN0 KEYIN1 KEYIN2 KEYIN3 KEYIN4

ONSWAn

VBATI_4.2V

64 63 62 61 60 59 58 7C_LED_VDD 57 56 55 54 53 52 51 VDIG_2.8V 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 CN962

C

KEYOUT1

UP

*

KB22

KEYOUT2

DOWN D

KB3

KB23

KEYOUT3

3

KB4

RIGHT

KB24

E KEYOUT4

SEND

BACK

CLEAER

KB5

KB10

GAME

LEFT KB25

KB20

KB15

KEYOUT5

MENU

MULTI

SEARCH

OK

CAM

F

KEYPAD VDIG_2.8V

HSMR-C191

R1130

FOLDER_DET

U1 A3212ELH 1 VDD 3 GND OUT 2

QSMR-C138 LD17

QSMR-C138 LD14

QSMR-C138 LD16

QSMR-C138 LD13

C26 0.1u

C25 0.1u

G

C21 10p

36

R1131

QSMR-C138 LD12

QSMR-C138 LD11

QSMR-C138 LD9

QSMR-C138 LD10 36

R1100

QSMR-C138 LD7

QSMR-C138 LD8

QSMR-C138 LD5

QSMR-C138 LD6 36

R1099

QSMR-C138 LD4

QSMR-C138 LD3

36

QSMR-C138 LD2

QSMR-C138 LD1

R1098

QSMR-C138 LD20

47

R1133

QSMR-C138 LD19

QSMR-C138 LD18

100K

G

FOLDER OPEN DETECTOR

KEY_LED-

H

Engineer:

KEYPAD BACKLIGHT BLUE LED

3G HANDSETS LAB. DEVELOPMENT GROUP 1 TITLE:

DOC CTRL CHK:

1

2

3

4

5

7

6

- 243 -

8

9

Date Changed:

Time Changed:

QA CHK:

Size:

U8100 KEY PT V1.3

A2

BB KEY PAD PCB 2004.02.09

MFG ENGR CHK: Changed by: mentor

H

LG ELECTRONICS INC.

Drawn by: R&D CHK:

REV:

12 1 8 A

Drawing Number:

Page:

FEB,17,2003

1

10

11

12

10. PCB LAYOUT

h lc

i b

o M

s ip

- 244 -

10. PCB LAYOUT

s ip

h lc

o M

i b

- 245 -

10. PCB LAYOUT

h lc

i b

o M

s ip

- 246 -

10. PCB LAYOUT

s ip

h lc

o M

i b

- 247 -